# SenseMaker

# IST2001-34712

Martin McGinnity University of Ulster Neuro-IT, Bonn, June 2004

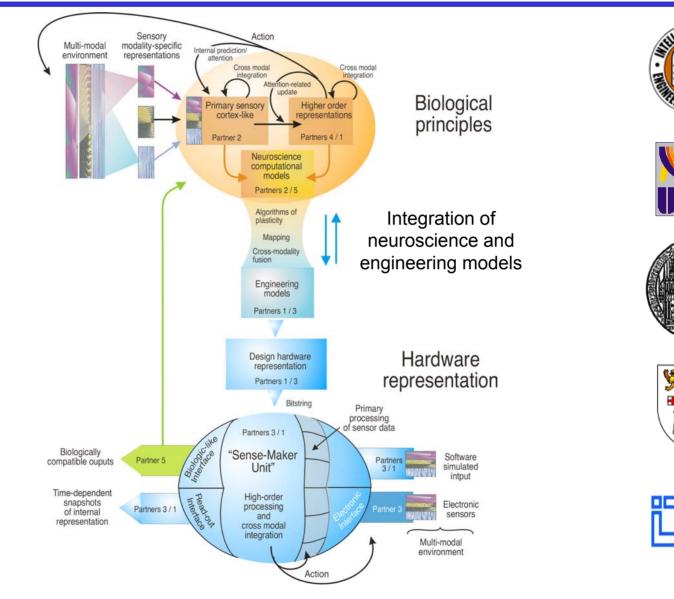

- To design and implement an intelligent computational system, drawing inspiration from biological principles of sensory receptor and nervous system function

- To conceive and implement electronic architectures that can merge sensory information from different modalities into a unified perceptual representation of the environment

- To explore a better understanding of information processing and function in the adult brain

- To achieve a higher level of communication between computer scientists, engineering, physics, psychology, and biological researchers

# **Overview of Project**

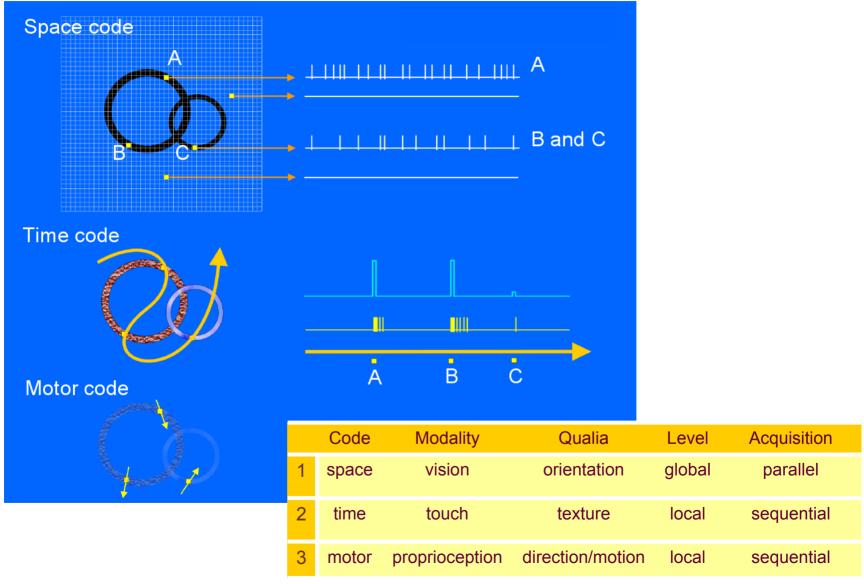

## Cross-modal integration: The Two-Ring Problem

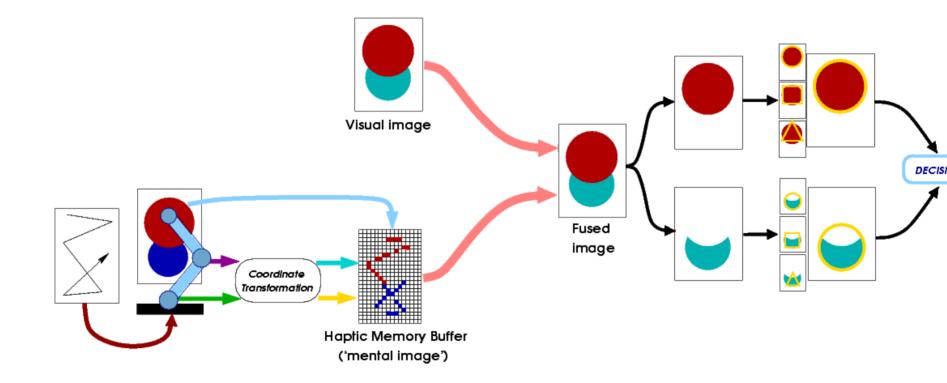

### Solving the Two-Ring Problem with the SenseMaker System

### Psychophysical Investigation of the 'Two-ring' problem

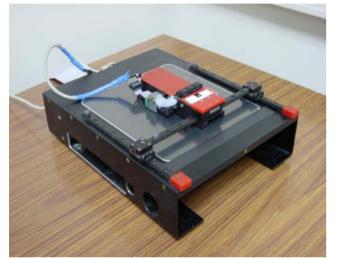

Apparatus: Virtual Tactile Display (VTD); developed by UHEI partners

0% vertical 50% vertical 100% vertical

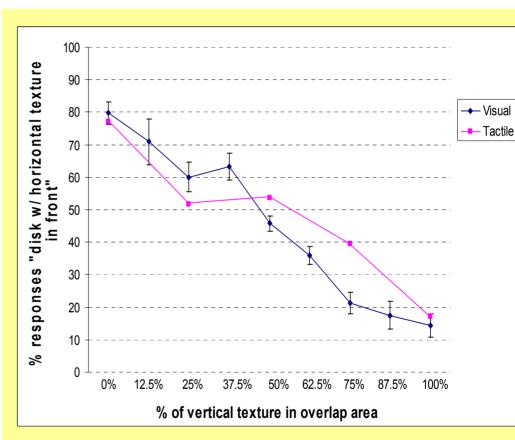

Results: Categorical perception of visual and tactile textur continua

Stimuli: Visual and tactile continua

## Silicon IC Neural Units

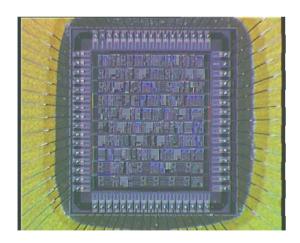

Custom circuits are developped to compute in real-time HH-like neuron and kinetic synapses models (analog design mode - Bipolar and MOS transistors - photograph: area of the die 4mmx3mm, 2k devices)

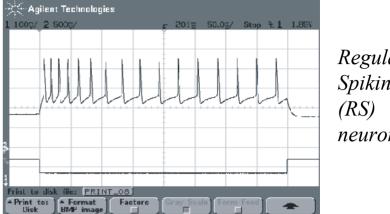

Spikin (RS)neuro

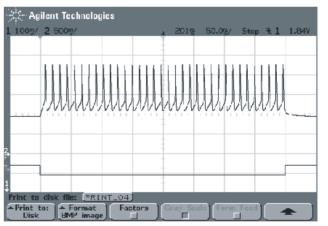

Fast Spikir (FS)neuro

Oscilloscope hardcopies: - Upper plot: membrane voltage output

-Lower plot: input stimulation voltage (inv. prop. to the stim. current)

# **SMU2 : FPNN Architecture**

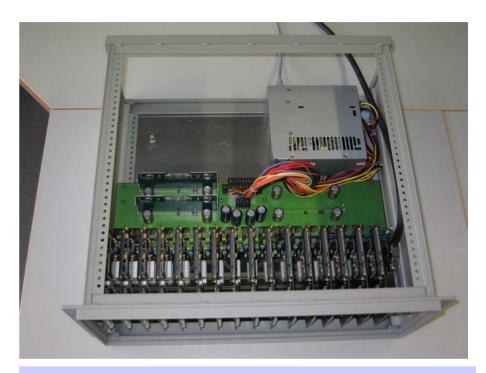

- a fully populated backplane has been produced

- Network tests are under way

- 16 Local PowerPC CPUs are running embedded Linux, total memory of up to 16 Gbytes

- FPNN ASIC interface on network module is working

- universal high-level software framework is available since July 2003 to configure and operate the SMU1, SMU2 and the later SMU3 system

- first experiments with SMU2 are in the preparation phase

#### The SMU2 system. One crate provides:

- 16 network modules

- 4096 binary neurons

- 524288 analog synapses

Largest full-custom hardware neural network ever build.

- technology: UMC 0.18µm, 6 metal, 1 poly

- 384 to 768 neurons, about 100000 synapses

- neuron model: modified integrate-and-fire with conductance based synapses

- fully analog network core

- time scale factor 10<sup>-5</sup>: 10 ns chip-time equals 1 ms in real-time

- short-term synaptic depression and facilitation: analog on-chip

- spike-time-dependent-plasticity: on-chip (analog measurement with digital weight adjustment)

- operation in the the SMU2 system framework

- independently programmable model parameters (at least E<sub>I</sub>, E<sub>x</sub>, E<sub>i</sub>, V<sub>t</sub>, V<sub>r</sub>, g<sub>m</sub>, t<sub>ref</sub>, t<sub>s</sub>)

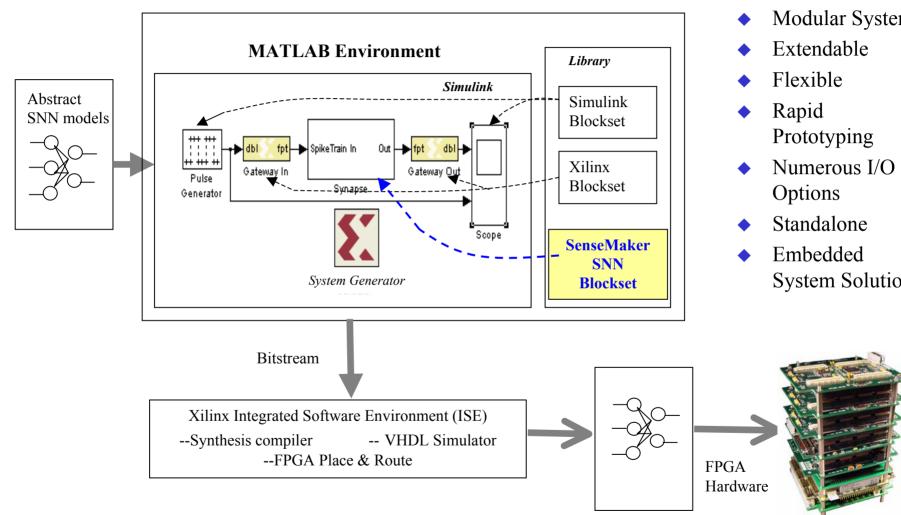

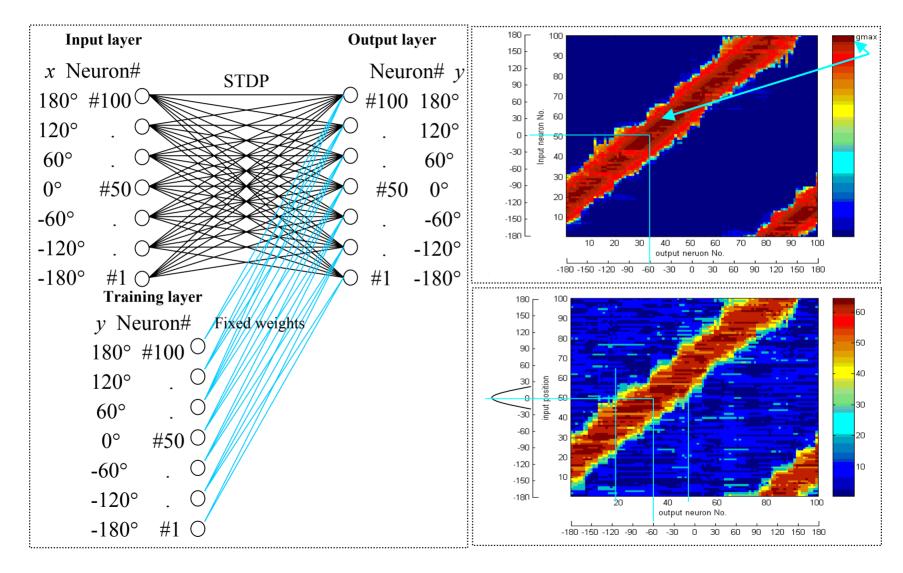

## **Design environment for Spiking Neurons and STDP on FPGAs**

**BenNuey PC104 Platform**

### **Example implementation of a module of the SenseMaker system - Matlab**

- Established a paradigm for comparing human and machine performance in merging of sensory codes

- Established task-dependent principles for higher level processing

- Developed an analog-digital simulator to translate biological model in ASIC representation

- Development of large scale spiking neural network, incorporating STDP learning, in analog ASIC

- Implementation of large scale spiking neural networks, incorporating STDP learning, in digital FPGAs – softwarehardware trade-off.